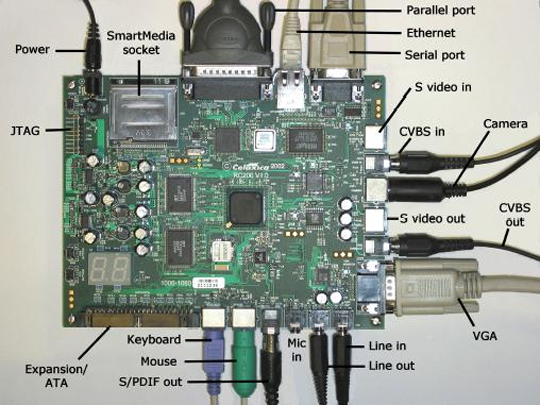

Graduation project at Philips TASS (now TASS Software Professionals), with the goal to design and implement a FPGA based video encoder and decoder application using the Celoxica RC200 (Xilinx Virtex II FPGA based) development board and the Handel-C hardware description language.

The FPGA video encoder and decoder are based on the RmaxCmax compression algorithm developed by Philips Research Laboratories. This compression algorithm uses discrete cosine transforms (DCT), like MPEG and JPEG. The algorithm transforms pixel blocks (of 8×4 or 8×8) into DCT coefficient blocks. The bit-planes of these DCT coefficient blocks (starting with the most significant bit-plane) are then compressed using zonal coding (meaning that only a small area of the bit-plane will be transmitted/stored). This data is then serialized in a way that the most significant data is transmitted/stored first. The resulting bit-string can be cut off at any length (to increase the compression), the remaining bit-string will produce the “best possible” image quality for the remaining data size.

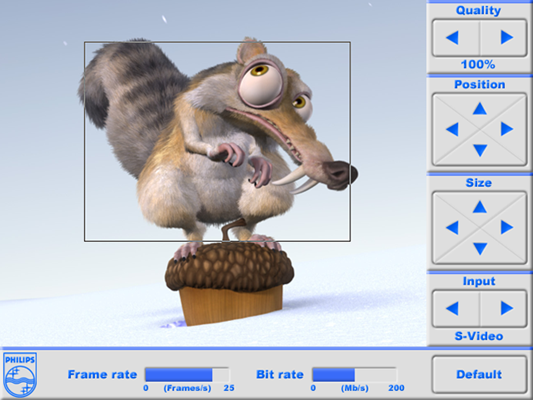

The graphical user interface (GUI) is programed within the FPGA itself, and provides the user with a fast and simple interface to view the encoding/decoding process and tweak the settings. The user can select a part of the video input, set the quality (read bit-rate), and can view the resulting decoded video output.